# ARQUITECTURA DE COMPUTADORAS

# Universidad Nacional del Sur

PRIMERA EDICIÓN: Marzo 2003

ÚLTIMA EDICIÓN: DICIEMBRE 2012

::: ACORDE A

ARQUITECTURA DE COMPUTADORAS PARA INGENIERIA

2DO CUATRIMESTRE 2012 :::

#### NOTAS:

0) EN LA PÁGINA 24 DEL PRESENTE DOCUMENTO SUGIERO ESTUDIAR EL APUNTE DE DIVISIÓN RÁPIDA SRT BRINDADO POR LA CÁTEDRA, ES LO ÚNICO QUE NO ESTÁ INCORPORADO EN EL RESUMEN. AL AGREGARLO SOBREESCRIBIR LA COPIA DE SEGURIDAD EN PDF.

- 1) ESTE RESUMEN PERMITE ALCANZAR UNA APROBACIÓN SEGURA DEL EXAMEN FINAL REGULAR SIEMPRE Y CUANDO SE LO ESTUDIE EN SU TOTALIDAD, LO CUAL QUEDA A TOTAL DISCRECIÓN DEL LECTOR

- 2) SI BIEN FALTAN ILUSTRACIONES (PEQUEÑOS ESQUEMAS Y DIAGRAMAS DE GANTT QUE COMPLEMENTEN LA TEORÍA), SE LAS PUEDE ENCONTRAR EN LA BIBLIOGRAFÍA DE LA CÁTEDRA.

- 3) SE BRINDA TOTAL DERECHO DE MODIFICACIÓN, AUNQUE SE PROVEE UNA VERSIÓN EN PDF COMO COPIA DE SEGURIDAD.

# Capítulo 1- Circuitos Digitales

#### **Teoremas**

```

-1a. 0.X = 0

1b. 1+X=1

- 2a. 1.X=X

2b. 0+X=X

- 3a. X.X=X

3b. X+X=X

-4a. X. not(X)=0

4b. X + not(X) = 1

-5a. X.Y = Y.X

5b. X+Y = Y+X

- 6a. X.Y.Z = X.(Y.Z) = (X.Y).Z

6b. X+Y+Z = X+(Y+Z)=(X+Y)+Z

-7a. \text{ not}(X.Y...Z) = \text{not}(X) + \text{not}(Y) + ... + \text{not}(Z). 7b. \text{not}(X+Y+...+Z) = \text{not}(X).\text{not}(Y). ... not (Z).

- 8. not f(X,Y,...,Z,...+)=f(not(X), not(Y),..., not(Z), +,..)

9b. (X+Y) . (X+Z) = X + (Y.Z)

-9a. X.Y + X.Z = X.(Y+Z)

- 10a. X.Y + X. not(Y) = X

10b. (X + Y).(X + not (Y))=X

-11a. X + X.Y = X

11b. X.(X + Y) = X

-12a. X + not(X). Y = X+Y

12b. X.(not(X) + Y) = X.Y

- 12a'. Z.X + Z. not(X). Y = Z.X + Z.Y

- 12b'. (Z + X).(Z + not(X)+Y) = (Z + X)(Z + Y)

- 13a. XY + not(X).Z + Y.Z = X.Y + not(X).Z

- 13b. (X+Y). (not(X) + Z).(Y + Z) = (X + Y)(not(X) + Z)

```

# Formas Especiales de Expresiones Booleanas

Hay cuatro formas especiales de expresiones Booleanas:

- Suma expandida de productos

- Producto expandido de sumas

- Mínima suma de productos

- Mínimo producto de sumas

La suma expandida de productos y el producto expandido de sumas son usados para el análisis de expresiones booleanas y están asociadas a circuitos y, también, son el punto de partida de otros métodos de simplificación. La mínima suma de productos y el mínimo producto de sumas son muy interesantes porque los circuitos son más frecuentemente implementados directamente por estas expresiones.

## Suma expandida de Productos (miniterm [1's de la función])

Aquí cada término contiene cada variable, complementada o sin complementar. Para obtener la suma expandida de productos desde una suma de productos, las variables perdidas son puestas en todas las posibles combinaciones de cada producto. Lo que se aplica es el teorema 10a en reversa

$$\sum (0,1,4,5) =$$

=  $not(A).not(B).not(C) + not(A).not(B).C + A.not(B).not(C) + A.not(B).C$

# Producto expandido de Sumas (maxiterm [0's de la función])

El producto expandido de sumas puede ser obtenido de un producto de sumas de la misma manera que en la suma expandida de productos. Las variables perdidas son puestas en todas las posibles combinaciones, a cada suma.

$$\Pi(2,3,6,7) = = (A+not(B)+C). \ (A+not(B)+not(C)). \ (not(A)+not(B)+C). \ (not(A)+not(B)+not(C))$$

#### Expresiones Booleanas Mínimas

El objetivo principal de la minimización de una expresión booleana consiste en llegar a una representación que corresponda a un costo mínimo de switch's en el circuito. Para este fin, el mínimo número de bloques lógicos es generalmente el criterio primario y el mínimo número de entradas en los bloques lógicos es típicamente el criterio segundo. Un bloque lógico esta compuesto de AND's y OR's. Se habla de AND seguido de OR en una suma de productos y de OR seguido de AND en un producto de sumas.

Una mínima suma de productos puede ser obtenida de una suma de productos por la aplicación de teoremas de simplificación. De igual manera se puede obtener un mínimo producto de sumas de un producto de sumas.

Una suma de productos puede ser obtenida de una expresión que no está en esta forma, "multiplying out" la expresión, es decir aplicando el teorema 9a en reversa.

Un producto de sumas puede ser similarmente obtenido por la operación dual de "adding out", es decir, aplicando el teorema 9b en reversa.

#### Método de Minimización

Los métodos de minimización se clasifican en tabulares o gráficos. El método de Quine–McCluskey es un método tabular. Los métodos Karnaugh y Veitch son métodos gráficos.

Ambos tipos de métodos no dan soluciones, bridan un punto de partida ayudando a determinar aquellos términos irreducibles. Salvo que el problema sea trivial, la obtención de la/s solución/es optimas requerirán de un proceso adicional.

#### **Combinaciones Opcionales**

Como sabemos, para una deseada función de un circuito, todas las combinaciones posibles de entrada pueden ser consideradas en dos grupos; un grupo consiste de aquellas combinaciones para las cuales se desea una salida, y en el otro grupo todas las combinaciones para las cuales no se desea ninguna salida.

Un ejemplo es:

- La salida es de la forma: not(A).not(B) + A.B.C

- No se desea salida en:

```

not(A).C + A.not(C) + A.not(B)

o

not(A).C + A.not(C) + not(B).C

```

Notar que la expresión de salida es el complemento de la de no salida

Ahora, todas las posibles combinaciones de entrada, pueden ser divididas en tres grupos:

- Un grupo consiste en aquellas combinaciones para la cual se desea una salida.

- Otro grupo son aquellas combinaciones para la cual no se desea una salida.

- Y un tercer grupo de combinaciones opcionales.

Estas combinaciones de entradas especiales pueden provenir de dos condiciones distintas:

- La combinación opcional es inválida, es sabido que nunca puede ocurrir.

- La combinación opcional es "don't care", es decir no influye en la salida si esta ocurre o no a la entrada.

No es necesario diferenciar entre combinaciones inválidas y don´t care; ambas tienen influencia en el circuito de la misma manera. Si una combinación opcional es adherida a una expresión booleana para la salida de un circuito, la expresión se puede volver más simple o más compleja.

# Minimización con el Método Tabular (Quine-McCluskey)

Este método se basa en el teorema X.Y + X.not(Y) = X

X representa una o más variables e Y representa una sola variable.

El primer paso es el de llevar la expresión a una suma expandida de productos. Este teorema es aplicado a exhaustivamente para llegar a los términos irreducibles.

Luego se separan de la tabla cada término en función de su peso (cantidad de 1's).

El tercer paso es comparar cada término de un determinado peso con todos los términos del peso siguiente. Si coinciden en todos los unos y solo no coinciden en un cero, se marcan como que se juntan y se crea una nueva tabla donde se tacha (-) el cero que no concuerdan.

Esto se hace hasta que no se puedan hacer coincidir ningún término con otro.

Cada término que queda al final se llama término irreducible.

Una vez terminado de encontrar todos los irreducibles, se crea una tabla donde cada columna son los términos de un principio y cada fila son los irreducibles.

Primero se elige cada terminal que sea el único y que cubra determinada columna luego se elige los terminales que cubran más columnas.

#### Solución algebraica para la tabla de implicantes primos

Una forma de realizar la selección de los mini términos es a través de una forma algebraica. Se le colocan una letra mayúscula a cada término irreducible y según quien cubra cada columna se realizan un productos de sumas donde cada suma son los mini términos que cubren cada columna. A través de aplicaciones de las propiedades y de los teoremas se reduce la expresión. Se llega a una suma de productos donde cada variable representa un término irreducible. Se elige uno de los términos de la suma de productos, dependiendo de la cantidad de entradas de cada término o de la cantidad de irreducibles que contenga.

# Diagrama Lógico Detallado

El diagrama lógico detallado es de interés principal para el fabricador y para el personal de servicio donde es usado, por ejemplo en testeo, mantenimiento, etc. El diagrama lógico detallado representa funciones lógicas y no

lógicas e incluye los aspectos físicos y eléctricos del circuito. El diseñador lógico debe saber como producir un diagrama lógico detallado de un diagrama lógico básico y como leer un diagrama lógico detallado.

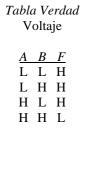

Las funciones lógicas son implementadas por circuitos lógicos o dispositivos. La información y las condiciones eléctricas se mantienen separadas de las funciones lógicas hasta este punto. Las entradas y las salidas de los circuitos lógicos debe encontrase en uno de dos estados. Estos dos estados, son típicamente dos valores de voltaje o niveles de corriente. Uno de los principales puntos aquí es relacionar el estado lógico 1 y 0 con, por ejemplo, el más alto o bajo nivel de voltaje. Esta relación, a la que llamamos "polaridad", es uno de los aspectos más importantes de el diagrama lógico detallado.

El nivel de voltaje es inmaterial; representamos el más alto (más positivo) de los dos nivel con H y el más bajo (el más negativo) de los niveles con L. Existen dos posibilidades:

- H representa 1 y L representa 0

- H representa 0 y L representa 1

Si pasa lo primero (H = 1, L = 0), un circuito o sistema se dice que tiene u opera con "lógica positiva". Si pasa lo contrario (H = 0, L = 1) se dice que el circuito o sistema tiene "lógica negativa".

Salvo que se indique lo contrario, por default las señales que entran o salen de un circuito se asumen en lógica positiva.

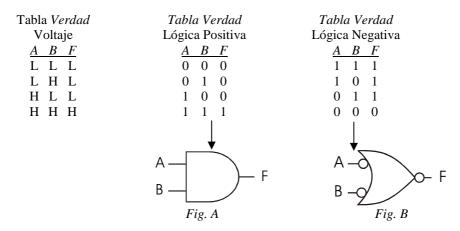

#### Circuito AND

La Fig. A es un diagrama detallado, donde la función AND es implementada con un circuito AND, con una lógica positiva.

La *Fig. B* es un diagrama detallado, donde la función AND es implementada con un circuito OR, con una lógica negativa. Se indica que es una lógica negativa a través de los círculos tanto a las entradas como las salidas.

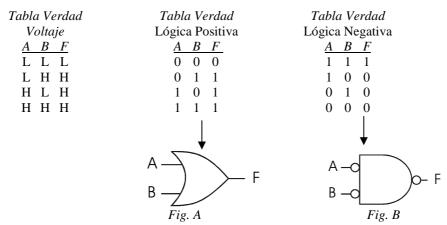

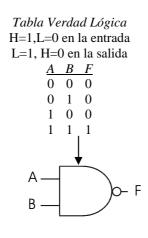

#### Circuito OR

#### Funciones NAND y NOR

Los circuitos más comunes son <u>NAND</u> y en menor medida <u>NOR</u>. El punto es que <u>no</u> es deseo del fabricante el and(or) negado. La cuestión es que para evitar la negación se debe introducir una etapa más de inversión, luego mayor retardo (NAND(2) 3 msg, AND(2) 6 msg). La idea para diseñar será emplear NAND y NOR en lógica mixta.

La función NAND tiene como salida 0 solo si todos las entradas son 1's. En manera inversa, la salida es solo 1, si alguna de las entradas, o más de una, son 0's. La función NAND es lo mismo que negar un AND común (Ej. not(X AND Y) = X NAND Y).

La función NOR tiene como salida 0 solo si una o más de las entradas son 1's. Inversamente, la salida es solo 1 si todas las entradas son 0's. La función NOR es lo mismo que negar el OR común. (Ej. **NOT**(X**OR**Y) = X**NOR**Y).

La álgebra de Boole puede ser realizada con solo funciones NAND o solo con funciones NOR.

| Tabla Verdad<br>Lógica |   |   |  |  |

|------------------------|---|---|--|--|

| A                      | В | F |  |  |

| 0                      | 0 | 1 |  |  |

| 0                      | 1 | 1 |  |  |

| 1                      | 0 | 1 |  |  |

| 1                      | 1 | 0 |  |  |

| ĺ | Tabla Verdad     |                  |   |  |  |  |  |

|---|------------------|------------------|---|--|--|--|--|

| l | Lógica           |                  |   |  |  |  |  |

| l | $\boldsymbol{A}$ | $\boldsymbol{B}$ | F |  |  |  |  |

|   | 1                | 1                | 1 |  |  |  |  |

|   | 1                | 0                | 0 |  |  |  |  |

|   | 0                | 1                | 0 |  |  |  |  |

|   | 0                | 0                | 0 |  |  |  |  |

F= NOT (A AND B) F= NOT(A) + NOT(B)

F= NOT (A OR B) F= NOT(A) . NOT(B)

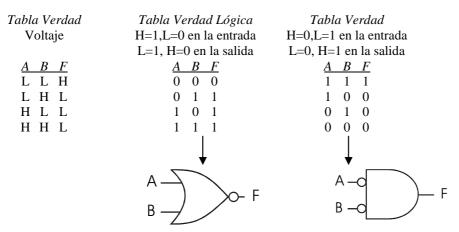

#### Circuito NAND

#### Circuito NOR

Una característica importante de los diagramas lógicos detallados, es que el diseñador puede mirar los símbolos e inmediatamente reconoce las funciones lógicas realizadas, sin conocerlas, sabiendo que tipos de dispositivos o que polaridad es usada para implementar la función. Por el lado contrario, mirando los símbolos y observando las funciones lógicas y las polaridades, se puede determinar no solo el tipo de dispositivo que se está usando, sino también los niveles de voltajes que se esperan.

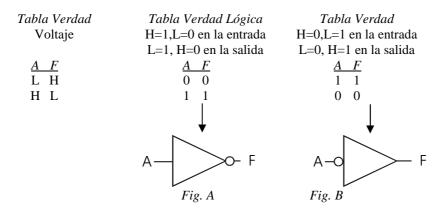

#### Circuito Inversor

Su rol es un cambio de polaridad en la lógica, NO la inversión lógica. La inversión lógica se logra con la discontinuidad en la polaridad asignada a una variable en su recorrido.

Este dispositivo tiene una entrada y una salida, con la característica que la salida es L solo si la entrada es H y la salida es H solo si la entrada es L. Para mantener la consistencia en el diagrama lógico detallado, desde el punto de vista de los niveles de voltaje, un circulo pequeño debe aparecer en la línea de la señal de entrada o en la línea de la señal de salida.

Diseño Lógico MSI y LSI

# El multiplexor Digital

Este dispositivo es llamado también "selector" ya que funciona muy parecido a una llave selectora. Por ejemplo, un multiplexor de ocho entradas selecciona una de las entradas para que sea la salida. Un código binario de tres bits determina que entrada aparecerá en la salida. Además es útil para simplificar funciones lógicas.

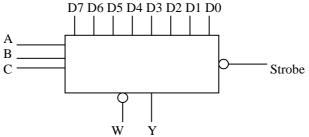

Fig. A Multiplexor de ocho entradas

La Fórmula de este sería

Y = ABC D7 + ABC' D6 + AB'C D5 + AB'C' D4 + A'BC D3 + A'BC' D2 + A'B'C D1 + A'B'C' D0

Aquí vemos que en este mux de 8 a 1, con 3 líneas de selección, pasamos de tener que implementar una función de <u>M</u> variables a 8 funciones residuo de M-3 variables que corresponden a la entrada de datos del integrado.

# El Decodificador o Demultiplexor

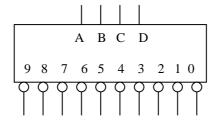

Es lo opuesto al multiplexor. En un decoder una dirección binaria de entrada determina cuál de las salidas será más baja (0). Por ejemplo en un decoder decimal la entrada es D'CBA'=0110 = 6 en decimal. Entonces la pata 6 del decoder será 0 y todas las demás serán 1. No se lo utiliza para seleccionar una de varias entradas, se lo emplea para implementar una función lógica. Con el decoder podemos reflexionar en cuanto a que cada salida del mismo es asimilable a un miniterm, de aquí lo podemos entender como una "familia" de miniterm.

#### Fig. A Decoder Decimal

Cabe aclarar que el decoder y el mux se complementan, esto es, el mux removiendo variables y el decoder en la implementación de funciones residuo.

#### Memorias de solo Lectura (ROM)

La ROM la podemos emplear en un proceso "estándar" de fabricación de circuitos combinacionales.

En las líneas de entrada presentamos las variables y se apuntara a una u otra locación según la combinación de verdadero/falso de las mismas.

Luego si en la función expandida (suma de productos) se tiene un dado miniterm, en la locación asociada se asocia un 1, 0 en caso contrario.

La programación se hará con la tabla de verdad (0's y 1's de la función), es por esto, que es un proceso estándar, no se sabe como es el circuito.

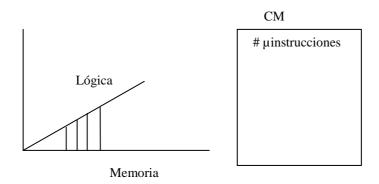

Si tenemos una ROM de n líneas de address tendremos 2<sup>n</sup> locaciones. De aquí se tiene que el tamaño de la ROM es 2<sup>n</sup> palabras si n es el número de variables. Cada locación es asimilable a un miniterm. Luego con n variables, tenemos 2<sup>n</sup> miniterminos y 2<sup>2^(n)</sup> funciones distintas. Esto induce a pensar que dada la ROM, esta admite infinitas funciones distintas por lo que es un hardware desproporcionado.

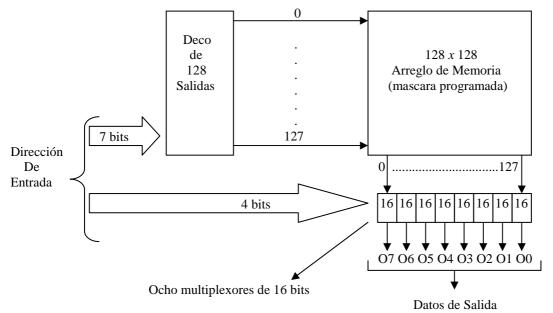

#### Reducción del tamaño de la ROM

Algo <u>muy</u> redituable sería codificar las entradas. Para cada variable que elimina la ROM pasa a la mitad de tamaño. Si podemos almacenar codificadas las salidas también podremos reducir el tamaño, pero ahora solo linealmente. Sin embargo, esto provoca que las ecuaciones lógicas se vuelvan más complejas.

También la podemos pensar a esta memoria de solo lectura como un arreglo de X-Y de puntos. Por ejemplo una ROM de 16.384 bits es un arreglo de 128x128 puntos. El circuito tiene ocho patas de salidas y 11 patas de entrada (direccionamiento). Por lo tanto está organizada como 2048 palabras de 8 bits cada una. Por esto, para cada combinación de entrada, se produce una salida diferente de 8 bits.

Fig. A ROM de 16.384 bits

#### Memorias de Solo lecturas Programables

La mayor desventaja de las ROMs programadas, es que es virtualmente imposible hacer algún cambio si un error se encuentra en el diseño. Por esto existen otros tipos de ROMs para producciones más pequeñas y para chequeos iniciales y producciones piloto.

Esta se llama Memoria de Solo Lectura Programable (PROM). Para programar el dispositivo, el usuario simplemente usa un Programador PROM, el cual escribe el bit deseado en el dispositivo. Algunas PROM son reprogramables, es decir que se pueden borrar eléctricamente o por exposición a una luz ultravioleta, y volverlas a escribir (EEPROM, EPROM).

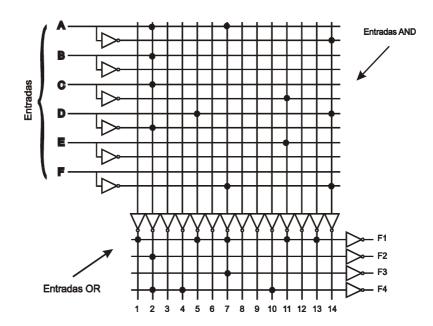

# Arreglos Lógicos Programables (PLA)

No es otra cosa que un AND seguido de OR. Con estas se especifica, no solo un bit de salida para cada word, sino la dirección del word. Esto hace posible tener más entradas que en una ROM del mismo tamaño.

Al igual que una ROM, podemos ver a una PLA como una memoria restringida, como un convertidor de código o como un generador de funciones lógicas. Además ambas matrices del PLA son especificadas por el consumidor mediante una tabla de verdad. La ROM también implementa una matriz que permite su decodificación dada una entrada. Tal como sucede con la ROM, los datos de la tabla de verdad se perforan en tarjetas que se utilizan para generar automáticamente una máscara especial en uno de los pasos de la fabricación de la PLA. En ambos integrados, generalmente es más económico decodificar salidas mutuamente excluyentes fuera del PLA con circuitos más económicos.

Lo que tenemos acá sería como una máquina de minitérminos. Las entradas son las variables y cada línea para abajo serían las variables que forman (mediante AND's) un término. Luego las líneas para la derecha que van hacia la salida son las uniones (OR's) de los minitérminos.

Además las redundancias se resuelven automáticamente. Es fácil observar como el layout de las matrices hace un uso muy eficiente del chip. El único factor a considerar es reducir el número de términos producto dado que el número de variables en cada término es irrelevante. Reducimos el número de términos productos solo hasta que se ajuste a las limitaciones del PLA, debido a que no existe beneficio alguno en obtener una reducción mayor.

Por ejemplo:

El la columna 2 tenemos el siguiente minitérmino: A B C D E F

El la columna 14 tenemos el siguiente minitérmino: A B C D E F 0 X X 0 X 0

En la fila F1 (la salida) tenemos: D + AF' + C'E

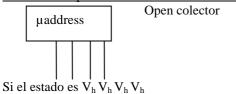

#### **Open Colector**

Existen situaciones en las que se plantean unir salidas entre sí. Ejemplo un bus.

En la comunicación, en el recurso compartido, se están uniendo salidas.

Una etapa de salida convencional no resistirá esta acción. La condición para que sea viable es que un nivel predomine sobre el otro.

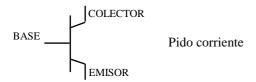

El elemento activo de un circuito electrónico es el transistor, ya sea bipolar o MOS.

En general al transistor se lo opera como una llave, como un contacto, abierto (OFF) o cerrado (ON). A estos estados se los conoce también como cortado o saturado respectivamente.

A continuación presentamos el esquema del transistor bipolar

A continuación presentamos el esquema del transistor MOS

Unir una o más salidas open collector

Si hay algún bajo el punto de unión es bajo. Sea alto si todos están en alto.

# LP <u>AND</u> WIRED LN <u>OR</u> WIRED

Indico que la salida de una compuerta es open collector

Si alguien escucha mal la información se corrompe. A través de un bit de paridad se detecta la falla. Es tolerante ante una falla, nada se quema.

Tiene aspectos positivos y negativos. Por un lado resiste <u>físicamente</u> a errores de habilitación. Por el otro es relativamente lento.

#### **Three State**

Habilita a disponer de varias salidas unidas entre si a condición de que:

- a) Todas estén en el tercer estado o

- b) Uno de ellos sea sacado del tercer estado

#### **Bus Three State**

En esta implementación de un bus por un lado se destaca su rapidez. Sin embargo, si hay habilitación múltiple el mismo falla. Si esto ocurre se debe arreglar la falla del direccionado y reemplazar el/los circuitos quemados. Se lo debe emplear dentro de una tarjeta o un chip. Además este esquema implementa de manera muy eficiente el multiplexado de señales.

Cabe aclarar que Three State no resuelve funciones lógicas.

# Lógica Secuencial

#### Elementos de Memoria

Aquí introduciremos el término de memoria cambiante. Si cambiamos el circuito dentro de una ROM, podemos cambiar los bits como queramos, y usarla para recordar cosas. La PROM es cambiable, pero no tan fácil como una RAM. Para cambiar el contenido de una RAM simplemente presentamos una muestra del bit deseado en la entrada de datos y pulsamos el reloj. La palabra es inmediatamente cambiada. La memoria nos permite recuperar todos los datos juntos en el instante en que se realiza el cómputo.

Al igual que tenemos compuertas lógicas como elementos básicos combinacionales y una ROM como un gran arreglo de elementos, tenemos los flip-flop como un elemento básico de memoria y una RAM como un gran arreglo de memoria. Esencialmente, compuertas y ROM's son análogos a flip-flops y RAM's, pero con flip-flops y RAM's tenemos la adición de la dimensión del tiempo. Ambos dispositivos tienen una entrada de reloj y sus estados cambian únicamente después de la transmisión del reloj.

#### Tipos de Flip-Flops

Los flip-flops se pueden definir a través de tablas de verdad y de diagramas, como los elementos combinacionales. En los flip-flops la salida siempre depende de la entrada. Como elementos de memoria, las salidas no cambian en función de la entrada hasta que el clock es transmitido.

• Flip-Flop D. Este es el flip flop Delay (retraso), y la ecuación muy simple nos dice que la entrada D es guardada en el flip-flop cuando ocurre el clock y aparece en la salida Q en el próximo tiempo de reloj. Este flip flop es muy parecido a una RAM de un solo bit, y es muy usada para guardar datos.

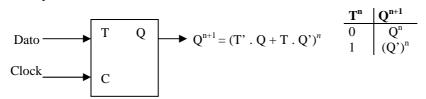

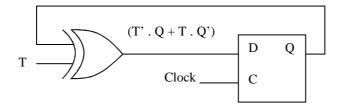

Flip-Flop T. Este es el flip-flop toogle. Este da como salida el estado anterior si la entrada T es falso antes del clock. Si la entrada T es verdadera, la salida cambia hacia el estado contrario con el clock. Este es muy usado para contadores binarios.

Flip Flop "T"

Cualquier flip-flop puede ser construido a través de un flip-flop D y usando algunas compuertas.

Ej. Flip-Flop T usando un flip-flop D.

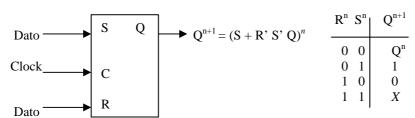

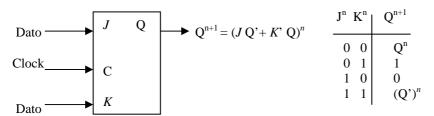

• Flip-Flop R-S, este setea después que la entrada S sea true y resetea después que la entrada R es true. La salida es indefinida si ambos R y S son true

Flip Flop "R-S"

• Flip – Flop *J-K*, este setea después que *J* sea true y resetea después que *K* sea true. Es similar al R-S salvo que si *J* y *K* son true, la salida cambia al estado contrario.

Flip Flop "J-K"

## **Master-Slave**

Se logra comportamiento de <u>tipo pulso</u>. Esto es, <u>la salida</u> cambiara luego de que la entrada (excitación haya desaparecido)

¿Por que en un registro de desplazamiento los flip-flops deben ser master-slave?

Cada flip-flop será leído y escrito simultáneamente. Es requisito para diseñar un circuito en modo pulso. Sino fuera MS cambiaria durante la exitación.

# Capítulo 2 – Algoritmos Aritméticos

#### Suma

```

Sean X = (X_{n-1}, ..., X_0) Y = (Y_{n-1}, ..., Y_0) Ambos de n dígitos y de una base b genérica. Luego X + Y = S = (S_n, S_{n-1}, ..., S_0) Y = (S_n, S_n) + (S_n) +

```

Se puede verificar que cualquier  $C_i$  será 0 o 1 ( $\Psi$  b). Considerando que  $X_i + Y_i \le 2$  (b-1) y con  $C_0 = 0$  (o eventualmente  $C_0 = 1$  si se restase en 2's complemento), el máximo valor para cualquier  $C_i$  será L(2(b-1)+1)/b = 1

En este algoritmo se analiza cada digito una vez. Por lo tanto, se dice que el algoritmo es de complejidad O(n). Una función g(n) es de complejidad de orden f(n) si para cualquier n,  $g(n) \le k$  f(n). Menos que n es imposible, al menos habrá que procesar cada digito. Luego los caminos de mejora se dan a nivel de implementación.

Para obtener el circuito lógico que resuelve la suma recurrimos a la tabla de verdad. Dado X<sub>i</sub>, Y<sub>i</sub>, C<sub>i</sub>

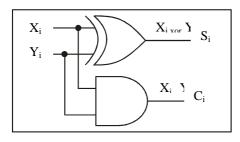

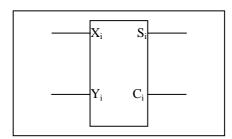

# Half Adder (HA, Semi Sumador)

Este toma dos operandos de entrada y produce dos salidas:

- $S_i$  = suma de los operandos =  $X_i$  XOR  $Y_i$

- C<sub>i</sub>= carry de salida = X<sub>i</sub>.Y<sub>i</sub>

Tabla de verdad

Xi

Yi

Si

Ci

0

0

0

0

0

1

1

0

1

0

1

0

Esquemático

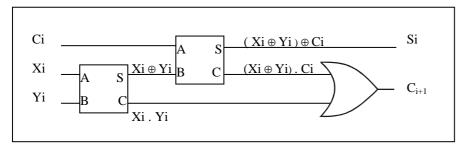

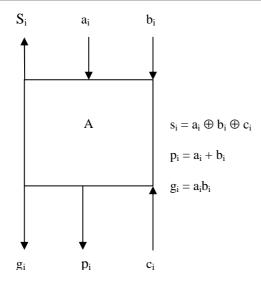

# Full Adder (FA, Sumador Completo)

Tomas tres entradas (los dos operandos y el carry de entrada) y produce dos salidas:

- $S_i$  = suma de los operandos con el carry de entrada =  $X_i$  XOR  $Y_i$  XOR  $C_i$

- $\bullet \quad C_{i+1} = Carry \ de \ salida = X_i.Y_i + (X_i + Y_i).C_i \ o \ equivalentemente$

- $C_{i+1} = Carry de salida = X_i.Y_i + (X_i XOR Y_i).C_i o equivalentemente$

|         | Tabla de verdad |         |         |           |  |  |  |  |  |

|---------|-----------------|---------|---------|-----------|--|--|--|--|--|

| $X_{i}$ | Yi              | $C_{i}$ | $S_{i}$ | $C_{i+1}$ |  |  |  |  |  |

| 0       | 0               | 0       | 0       | 0         |  |  |  |  |  |

| 0       | 0               | 1       | 1       | 0         |  |  |  |  |  |

| 0       | 1               | 0       | 1       | 0         |  |  |  |  |  |

| 0       | 1               | 1       | 0       | 1         |  |  |  |  |  |

| 1       | 0               | 0       | 1       | 0         |  |  |  |  |  |

| 1       | 0               | 1       | 0       | 1         |  |  |  |  |  |

| 1       | 1               | 0       | 0       | 1         |  |  |  |  |  |

| 1       | 1               | 1       | 1       | 1         |  |  |  |  |  |

Full Adder a partir de dos Half Adders

Circuito Lógico

Para sumar n bits lo que se hace es: empezar por la posición 0, pongo de entradas  $X_0, Y_0$  y  $C_0$ . Esto me da el digito  $S_0$  de la suma y utilizo el  $C_{out}$  para el  $C_{in}$  de la posición 1, y así hasta llegar hasta la posición n-1. (Orden (n)).

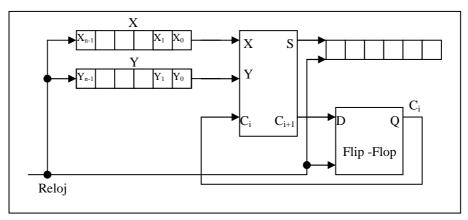

**Sumador Serie**: Un circuito para sumar n dígitos, muy básico, sería un sumador serie con un único Full Adder y un Flip-Flop; en la medida que se entreguen de manera serial los  $X_i$  e  $Y_i$  y se vayan almacenando los  $S_i$  resultantes.

Los sumadores seriales no son usados en el diseño de procesadores centrales o ALU's debido a que son muy lentos y también muy restrictivos.

Un ejemplo de este tipo yace en un controlador de disco, el RR06 (DEC). El disco decidía que cilindro alcanzar de forma serial, de manera serial realizaba la diferencia.

#### **Sumadores Paralelos**

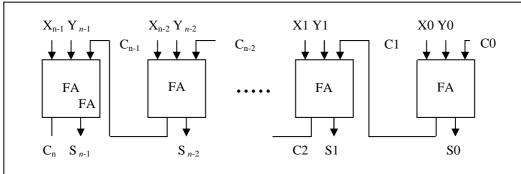

• **Ripple Adder**. Es el más simple. Consiste de n F.A. donde el carry de entrada a un F.A. es el carry de salida del F.A. precedente.

$$C_{i+1} = \underbrace{X_i \cdot Y_j}_{g_i} + \underbrace{(X_i + Y_i) \cdot C_i}_{carry}$$

$$carry carry$$

$$generado propagado$$

Cabe aclarar que si los dos operandos son 1, se genera carry independientemente del carry de arrastre. El tiempo de suma dependerá del valor particular de los operandos.

La situación más crítica en cuanto a disponer del carry de entrada es todos propagando y ninguno generando.

En este caso la complejidad es O(n).

Si operase en forma sincrónica deberé considerar para el tiempo el del peor caso. Asincrónicamente, detectando cuando termina la suma se verifica que el tiempo promedio es proporcional al  $\log_2(^{5n}/_4)$ .

Sin embargo, operar asincrónicamente no interesa por:

- a) Complica el control

- b) Un compilador optimizante no podrá tomar provecho de ello.

En particular, la suma (resta) es una operación básica que determinara muy posiblemente el periodo del reloj.

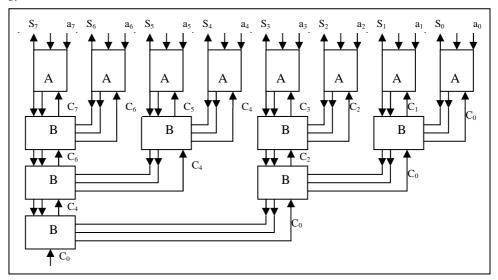

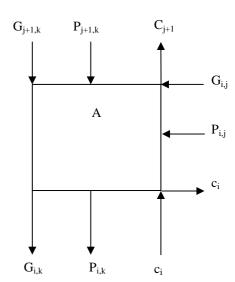

#### • Carry Look-Ahead Adder.

Podemos comparar la circunstancia de tener un tiempo de suma proporcional a 2n (pensando que cada F.A. implica <u>2</u> niveles de compuertas) con el hecho de que una función lógica se resuelve con <u>2</u> niveles AND seguido de OR u OR seguido de AND.

La respuesta a este planteo es "generar" el carry como una función independiente de la suma (De allí el nombre CLAA).

Luego tengo una función lógica para obtener el carry en los diversos full adders en la cual interviene los Xi e Y<sub>i</sub> de las posiciones anteriores y el carry inicial.

En cuanto a lo que retardo respecta tenemos:

1 nivel para computar G y P.

1 nivel para resolver los productos lógicos

1 nivel par resolver la suma lógica

3 niveles para determinar los carry de entrada a los F.A. + 2 niveles para la suma en sí

Por lo tanto, la suma se resuelve en  $\underline{5}$  niveles de compuertas cualquiera sea n, muy distinto de los 2n del ripple.

La cuestión es que este planteo encuentra "rápidamente" limitaciones prácticas por:

- a) Cuestiones de fan in

- b) Cuestiones de fan out

- c) Cuestiones de layout (caminos de interconexión largos e irregulares) que lo tornan, impracticable con n que supere valores 4-5.

¿Cual es la salida a esto?

Sin apartarnos ápice de la idea (de carry por adelantado) el recurso será generar los p y g en etapas, esto es, instanciar la obtención de los mismos. No resolverlos en un nivel sino en varios niveles lógicos pagando el precio de <u>un mayor</u> retardo pero haciéndolo técnicamente rentables.

Si observamos las ecuaciones de P, G y C podemos obtener las siguientes relaciones recursivas:

1.

$$C_{k+1} = G_{ik} + P_{ik}$$

.  $C_i$  con  $i < j$ ,  $j+1 < k$   $i$   $j$   $k$

2.  $G_{ik} = G_{j+1k} + P_{j+1k}$ .  $G_{ij}$

3.  $P_{ik} = P_{ij}$ .  $P_{i+1k}$

Estas ecuaciones también valen si  $i \le j$ , j < k, si asumimos  $G_{ii} = g_i$ ,  $P_{ii} = p_i$

A modo de ejemplo veamos expresar  $P_{03}$  y  $G_{03}$

$$\begin{split} &P_{03} = P_{01} \text{ . } P_{23} = P_{00} \text{ . } P_{11} \text{ . } P_{22} \text{ . } P_{33} = p_0 p_1 p_2 p_3 \\ &G_{03} = G_{23} + P_{23} \ G_{01} = (G_{33} + P_{33} \ G_{22}) + P_{22} \ P_{33} \ (G_{11} + P_{11} \ G_{00}) = g_3 + p_3 g_2 + p_3 p_2 g_1 + p_3 p_2 p_1 g_0. \end{split}$$

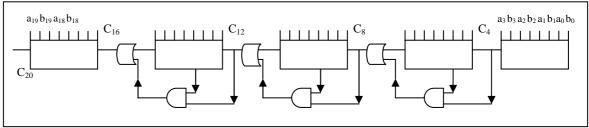

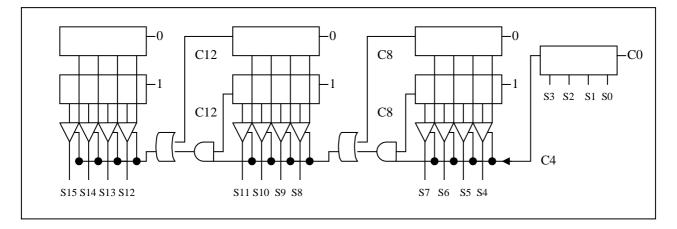

Con esto se puede construir un CLA práctico. El sumador consiste de dos partes. La primera computa los valores de P y G. La segunda usa estos valores de P y G para calcular los Carries. Dejando propagar las señales en los niveles expresados, se plantea recorrer el camino inverso a partir del  $\underline{C}_o$  y de los P y G que fueron calculados en la primera instancia.

Los bits en un CLA deben pasar a través de  $\log n$  niveles lógicos, comparados con  $\log 2n$  del ripplecarry adder. Mientras que el ripple tiene n celdas, el CLA tiene 2n celdas, que usan un tamaño de  $n.\log(n)$ . Esto es lo que se paga por un incremento en la velocidad, espacio. Sin embargo, conserva una estructura regular lo que favorece la integración a gran escala.

Sea n=8:

Existen alternativas, no tan costosas como el CLAA, pero de performance superior a la del ripple y algo inferior a la de este.

Básicamente construimos con pequeños sumadores ripple (de algunos pocos bits) sumadores complejos apelando a dos alternativas posibles:

- a) Carry Skip Adder

- b) Carry Select Adder

- Carry Skip Adder. Este está situado en el medio de ripple y CLA, en términos de velocidad y costo. La idea de este sumador comienza con el hecho que computar el propagado (P) es mucho más simple que computar el generado (G), por lo tanto el carry skip adder solo computa el propagado. Esto surge de la salida de carry del propio sumador, a partir de forzar inicialmente C<sub>in</sub> = 0 con lo que <u>luego</u> del tiempo de suma el C<sub>out</sub> no es otra cosa que el carry generado por el bloque. Para analizar la velocidad, asumimos que toma 1 unidad de tiempo pasar la señal a través de dos niveles lógicos. Entonces si tenemos, por ejemplo, que sumar 20 bits, en bloques de 4 bits cada uno

tenemos:

- 4 unidades de tiempo para producir todos los propagados y el primer carry in (del primer bloque).

- (n/k 2) unidades de tiempo para pasar el bloque, es decir, (20/4 2) = 3 unidades de tiempo

- 4 unidades de tiempo para que el último bloque realice la suma.

Esto nos da 11 unidades de tiempo para realizar la suma.

Una variante para mejorar el tiempo es tener bloques de distinto tamaño de bits. Resulta beneficioso ensayar ir aumentando hacia el centro en la idea de que la propagación del carry se va retrasando, dando luego posibilidad de mayor tiempo para generación sin prejuicio de temporizado. A su vez conviene que los sumadores más alejados sumen menos bits (porque su carry se resuelve más tarde).

Por ejemplo si, en el caso anterior, tenemos el primer bloque de 2 bits, el segundo de 5 y los restantes de 6, 5 y 2 bits, el tiempo total se reduce a 9 unidades de tiempo.

¿Con equispartición dado n hay algún valor óptimo para m?

Retardo = Tiempo suma primero (coincide con la generación de los restantes) + Tiempo en hacerse del carry del último sumador + Tiempo de suma de este

$$= m t + (n/m - 2) t + m t$$

Retardo = (n/m + 2m - 2) t

Derivamos respecto a m  $\delta/\delta$  m (n/m + 2m -2) t = n/m<sup>2</sup> -2 = 0 entonces m=  $\sqrt{(n/2)}$

Justamente con n=32 da 28t y con n=128 da 60t

Así Si n=32 m=4 Si n=128 m=8

Este circuito tiene una complejidad en tiempo del orden de  $O(\sqrt{n})$ .

• Carry Select Adder. Este trabaja con el siguiente principio: se realizan dos sumas en paralelo, una asumiendo carry in 0 y la otra asumiendo carry in 1. Cuando el carry es finalmente conocido, se selecciona la suma correcta. Con este método obtenemos el doble de velocidad con un costo de 50% más. Sin embargo los carry's deben atravesar varios multiplexores, los cuales incorporan un retraso. Para aprovechar esto, una variante es que cada bloque sea un bit más grande que su antecesor. Esto produce que se necesiten bloques de varios tamaños, por lo tanto no conviene equispartición, en su lugar, una rampa.

El retardo puede calcularse, despreciando el retardo de los multiplexores, como:

Retardo = m + (n/m – 2) y la complejidad en tiempo es también  $O(\sqrt{n})$ .

| Sumador    | Tiempo        | Espacio       |

|------------|---------------|---------------|

| Ripple     | O(n)          | O(n)          |

| CLA        | $O(\log n)$   | $O(n \log n)$ |

| Carry Skip | $O(\sqrt{n})$ | O(n)          |

| Carry      | $O(\sqrt{n})$ | O(n)          |

| Select     |               |               |

Comparación de los Tipos de Sumadores

# Multiplicación de enteros no signados

```

Sean x, y y p el multiplicando, multiplicador y producto respectivamente.

```

$X = (X_{n-1}, ..., X_0)$  e  $Y = (Y_{n-1}, ..., Y_0)$  en una base b posicional.

Su producto P es un numero de 2n digitos,  $P=(P_{2n-1},\,P_{2n-2},\,...,\,P_0)$ , los cuales se obtendrán como sigue:

La complejidad del algoritmo es O(n²). Esto indica que a nivel del algoritmo habrá mucho para hacer (cosa que no ocurre con la suma). Mucho se ha investigado sin precisar cuan cerca de O(n) se puede estar. El punto es que en la mayoría de los casos resulto de interés teórico más que practico.

#### Mejora del algoritmo

Si dividimos multiplicador y multiplicando en mitades:

$$\begin{split} X &= (X_1 \ 2^n + X_0) \\ Y &= (Y_1 \ 2^n + Y_0) \\ X_1 &= (X_{2n-1}, \ \dots, \ X_n), \ X_0 = (X_{n-1}, \ \dots, \ X_0) \end{split}$$

Gráficamente

$$P = X \cdot Y = (2^{2n} + 2^n) X_1 Y_1 + 2^n (X_1 - X_0) (Y_0 - Y_1) + (2^n + 1) (X_0 Y_0)$$

Estamos reemplazando un producto de operandos de 2n bits por tres productos de operandos de n bits.

$$[T(2n) \le 3T(n) + C_n]$$

C se relaciona con sumas y corrimientos

La solución a esta ecuación es que  $T(n) \le 3 C_n^{\log 3}$ , esto es, de  $O(n^2)$  se pasa a  $O(n^{1.59})$ .

#### Circuito Básico

A acumulador

MQ multiplier - quotient

Concatenados con capacidad de corrimiento a derecha

A = 0

MQ = Y (multiplicador)

B = X (multiplicando)

En cada iteración se analiza el bit menos significativo de MQ.

Si 1 sumo A+B y corro (con carry) a derecha

Si 0 simplemente corro

Y así hasta iterar n veces con lo que en AMQ queda el producto de X e Y

# Multiplicación de enteros signados

Si es signo magnitud, el mismo hardware funciona.

Consideramos  $X = (X_{n-1}, ..., X_0)$  e  $Y = (Y_{n-1}, ..., Y_0)$  donde  $X_{n-1}$  e  $Y_{n-1}$  son los dígitos del signo.

Luego  $P = (P_{2n-1}, P_{2n-2}, P_{2n-3}, ..., P_0)$

$P_{2n-3} \dots P_0$  sale de hacer  $X_{n-2}, X_{n-3}, \dots, X_0 \cdot Y_{n-2}, Y_{n-3}, \dots, Y_0$

$P_{2n-2} = 0$

$P_{2n-1} = X_{n-1} XOR Y_{n-1}$

En notación 2's complemento recordando que un numero negativo x es un numero positivo de valor  $2^n$  - |Y|, si aplicamos el hardware visto tanto con Y < 0 como X < 0 se induce a error!

#### Caso A

$$X < 0$$

$P = X \cdot Y = 2^{n-x} \cdot Y = 2^n Y - |X| Y$

$Y \ge 0$

El resultado correcto es un numero negativo menos  $\begin{bmatrix} X \\ 2^{2n} - \end{bmatrix}$ . Y  $\begin{bmatrix} 2^{2n} - \end{bmatrix}$   $\begin{bmatrix} X \\ Y \end{bmatrix}$

Para corregir el resultado tenemos dos posibilidades

a) Proceder como se vio, sin cambio (normalmente), y corregir al finalizar  $P+2^{2n}-2^n$   $Y=2^n$   $Y-\left[X\right]Y+2^{2n}-2^n$   $Y=2^{2n}-\left[X\right]Y$

b) Asumir X de doble extensión

$$P = (2^{2n} - |X|)Y = 2^n Y - |X|Y = 2^{2n} (Y-1) + 2^{2n} - |X|Y$$

Dado que en 2's complemento el carry se descarta

Observar que esto no implica A y ALU de 2n bits, la extensión es virtual. Se implementa trabajando con el bit que ingresa a AMQ (por izquierda) que no será el de carry. Sino:

#### Caso B

$$\begin{array}{ll} Y<0 & P=(2^n - \left| \right. Y \left| \right. ) \ X=2^n \ X - \left| \right. Y \left| \right. X \\ X\geq 0 & \end{array}$$

- a) Sumar  $2^{2n} 2^n \mid X \mid$

- b) Asumir Y de doble extensión (2n bits)

La opción b implica el doble de iteraciones. Luego claramente conviene la opción a

Luego el resultado correcto es  $2^{2n}$  -  $\mid Y \mid X$

#### Recodificando el multiplicador

Durante la implementación y con objeto de acelerar el proceso de multiplicación se puede recodificar de a más de un bit del multiplicador (Y). Si recodifico de a c bits tendré n/c iteraciones y deberé disponer de 2° múltiplos de X.

La recodificación de Booth propone trabajar en digito signado para el multiplicador.

Para justificar esta operación consideremos una subcadena de 1's en el multiplicador de la forma (X es 0 o 1):

(posición)

i(i-1)

La contribución al producto de este String de 1's es:

$$x*(2^{i}+2^{i+1}+...+2^{j-1})=x*(2^{j}-2^{i})$$

Reemplazo el string de 1's por una resta al principio y una suma al final. Observar que en 2's complemento la resta se resuelve tan fácil como la suma. Se necesita un flag para controlar si sumar, restar o saltear.

Reestructurando el algoritmo:

Es de observar que en la operación <u>producto</u> si trabajamos de forma "asincrónica" se podría tomar ventaja de las posibilidades que da el multiplicador a nivel de

- a) Shift Over Cero's (correr sobre 0's.)

- b) Skip Over Cero's (saltar sobre 0's.)

Skip Over Cero's asegura:

- Poder detectar una cadena de 0's

- Disponer de una unidad de corrimiento variable

En operación sincrónica, ¿Cuál es el aporte de Booth?

1. Resuelve de forma automática el caso y < 0 trabajando en 2's complemento. Esto resulta del hecho de que el bit signo es 1 y la extensión de signo virtual es como una cadena de 1's. Bastara que en el proceso de análisis del multiplicador (codificado según Booth) no vea la finalización del String de 1's para que al no hacer la suma respectiva estaré efectivamente restando  $2^n x$  que es lo mismo.

El peor caso es no saltear sobre 0's cuando se implementa la versión original del algoritmo. Cuando el multiplicador es la forma 0101...0101 y saltamos sobre 0's y 1's, aún tenemos que realizar n operaciones. Esto es porque a veces el decodificador realmente revisará si es un solo 1 rodeado de 0's para realizar solo una suma en lugar de una suma y una resta. Si podemos saltar sobre 0's en cualquier longitud, se demuestra que los desplazamientos promedio son de un largo de 2. Si pueden saltarse 0's y 1's, entonces el promedio sube a 3. Pero la circuitería necesaria para implementar saltos variables de cualquier longitud puede ser muy engorrosa.

Una alternativa a saltar sobre 0's y 1's es recodificar c bits del multiplicador a la vez y tener  $2^c - 1$  múltiplos del multiplicando antes de comenzar la multiplicación. Por ejemplo, con c = 2, tendríamos x, 2x y 3x. Si los bits  $y_i$  e  $y_{i+1}$  del multiplicador son 00, se realiza un desplazamiento doble a derecha. Si son 01, entonces se suma x antes del desplazamiento. Si son 10, sumaremos 2x y si son 11 3x. En el paso 2 del algoritmo original, i es incrementado en 2. Hay dos esquemas, mirar al futuro o soportarse en el pasado.

| Mu        | Multiplicador |       | Multiplicador Producto agregado |                                |  | Explicación |

|-----------|---------------|-------|---------------------------------|--------------------------------|--|-------------|

| $y_{i+2}$ | $y_{i+1}$     | $y_i$ |                                 |                                |  |             |

| 0         | 0             | 0     | 0                               | Sin cadena                     |  |             |

| 0         | 0             | 1     | +2                              | Fin de cadena de 1's           |  |             |

| 0         | 1             | 0     | +2                              | Un solo 1                      |  |             |

| 0         | 1             | 1     | +4                              | Fin de cadena                  |  |             |

| 1         | 0             | 0     | -4                              | Comienzo de cadena             |  |             |

| 1         | 0             | 1     | -2                              | +2 por final y -4 por comienzo |  |             |

| 1         | 1             | 0     | -2                              | Comienzo de cadena             |  |             |

| 1         | 1 1 1 0       |       | 0                               | Cadena de 1´s                  |  |             |

Recodificación del multiplicador de 2 bits con salto

Este esquema de recodificación puede implementarse con saltos sobre 0's y 1's. La Tabla 1 muestra cómo esto puede realizarse simultáneamente para 2 bits con la generación de solo 2x y 4x, o sea, solo desplazando el multiplicando a izquierda. Para entender la tabla debemos poner atención al hecho de que los bits  $y_i$  e  $y_{i+1}$  son los recodificados, mientras que el bit  $y_{i+2}$  se usa para indicar la terminación posible de una cadena. Además se asume que hay dos bits 00 extras implícitos en el final menos significativo y otro en el extremo izquierdo. Por ejemplo, un multiplicador de 6 bits (011001) = 25 es recodificado como:

bit extra bits extras

$$-4.2^{-2}.x$$

$2.2^{0}.x$   $-2.2^{2}.x$   $2.2^{4}.x$

que es (32-8+2-1).x = 25x

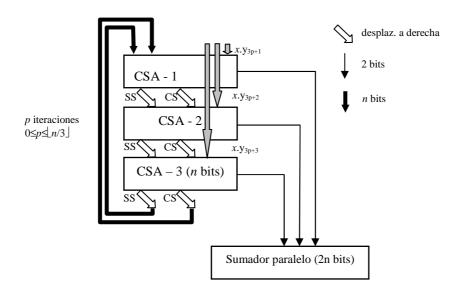

# **Usando CSA**

En realidad no es un sumador paralelo. Si tenemos operandos de n bits un CSA se constituye con n F.A desconectados entre sí. <u>No</u> hay procesamiento de carry alguno.

La entrada  $C_{in}$  de los F.A. se destina a un tercer operando, luego al CSA entran 3 operandos y entrega dos resultados:

- Pseudosuma

- Pseudocarry

La verdadera suma se alcanza si hacemos la suma de estas dos sumas.

## **Ejemplo**

El tiempo de ejecución es mínimo, corresponde a un F.A. (<u>ni</u> carry anticipado, <u>ni</u> ripple, el C<sub>in</sub> es un operando). Si hay que sumar tres o más operandos resultara ventajoso el empleo de estos "sumadores", ejemplo de esto el producto. Para tal fin, podemos usar el siguiente algoritmo:

```

1. ss_{j} = 0, cs_{j} = 0, 1 \le j \le 2n

2. for i=1 to n

if y_{i} \ne 0

for k=0 to (n-1)

3. ss'_{i+k} = ss_{i+k} \oplus cs_{i+k} \oplus x_{i}

cs'_{i+k+1} = ss_{i+k} *cs_{i+k} + (ss_{i+k} \oplus cs_{i+k}) *x_{i}

ss_{i+k} = ss'_{i+k}

cs'_{i+k+1} = cs'_{i+k+1}

end

```

4. Sumar ss y cs en un sumador convencional de 2n bits.

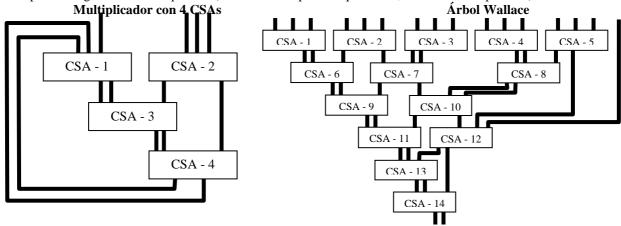

Como los CSAs son mucho menos complejos que los sumadores paralelos, podemos usar más de uno sin un incremento indebido en el costo. En la figura se muestra cómo usar los CSAs

En una fase de reloj las operaciones de cada CSA, menos la última suma ripple, toma *n* niveles de CSA. No parece haber ventajas entre colocar 1 o 3 CSAs. Pero si permitimos superponer las operaciones, por ejemplo, realizar la recodificación del multiplicador en paralelo con la acumulación de productos parciales, el duplicar hardware implica una gran mejora. Además, si incrementamos el número de CSAs, podemos realizar concurrentemente partes del proceso de multiplicación. En la figura, mostramos cómo la inclusión de un CSA más permite algunas sumas en paralelo(solo una descripción esquemática, sin el sumador paralelo).

El número de iteraciones se decrementa de n/3 a n/4 para un tiempo total de 34n niveles de CSAs. Más generalmente, si tenemos (n-2) CSAs podemos construir un árbol de profundidad de  $O(\log n)$ , o sea, genera la suma de las sumas ripple en  $O(\log n)$  niveles de CSAs. Este orden de magnitud se obtiene de la siguiente construcción. Agrupamos de a n operandos en tríos como entradas a los CSA superiores. Se obtienen (aproximadamente) 2/3.n salidas, las cuales alimentan de nuevo en tríos al segundo nivel. Continuando la construcción hasta tener solo 2 salidas. Evidentemente tenemos profundidad logarítmica, ya que decrementamos el número de entradas un tercio cada nivel. Se necesitan (n-2) CSAs, y se prueba por inducción sobre el número de operandos. Esto se llama Wallace Tree o sumador Wallace.

En general, no deseamos invertir en (n-2) CSAs. Pero solo un número limitado de ellos pueden ser conectados como en la figura y emplear un algoritmo iterativo. Recodificar el multiplicador puede usarse concurrentemente, con dos desplazamientos (o más) en lugar de uno.

La suma es computada por el árbol de CSAs, el cual produce una suma de 2n bits y un carry de 2n bits. La absorción final del carry es elaborada por un sumador paralelo con propagación interna de carry.

El multiplicador estrictamente combinacional de la figura es práctico para valores moderador de n, dependiendo del nivel de integración que se use. Para valores de n grandes, el número de CSAs necesarios se vuelve excesivo. Las técnicas de CSAs pueden seguir usándose sí particionamos el multiplicador en k segmentos de m bits. Se repite el proceso k veces y se va acumulando el resultado. El resultado se obtiene por lo tanto luego de k iteraciones. La multiplicación carry-save es apropiada para implementaciones pipelined.

#### **VLSI**

La alternativa para alcanzar profundidad logarítmica en n (log n) es el árbol binario del producto.

Se necesita ya no un sumador (3,2) como el CSA sino uno (2,1) entran dos bit suma y sale un bit.

¿Y el carry? La notación digito signado hace posible la suma sin carry. El precio que se paga, como se verá, es:

- a) Se necesita un doble registro para almacenar (1, 0, -1)

- b) La lógica de suma es más compleja que la del CSA, en el cómputo de S<sub>i</sub> en una dada posición intervienen no solo los bits de la posición i sino que además los de la posición i-1 o i-2.

Esto último, no obstante, es de mucho menor alcance que en el caso de una suma convencional (con carry) donde se debe considerar desde la posición i hasta la inicial 0.

# Desarrollamos el algoritmo en 2 pasos:

a) En un primer paso calculamos los  $S_i$  y  $C_{i+1}$  para que en un paso siguiente, en el que se computa  $S_i$  +  $C_i$  (resultante del anterior) no se genere carry en las diversas posiciones. Según tabla se calculan los  $S_i$  y  $C_{i+1}$  y luego se acomete la suma entre  $S_i$  y  $C_i$ , como sigue:

$$\begin{array}{ccc} X_i & S_i \\ \underline{Y_i} & \underline{C_i} \\ S_i & \underline{S_i} \end{array}$$

Se tendrá la siguiente tabla para  $X_i + Y_i$

| $X_{i}$          |   | 1 |   | 1      |    | not(1) |   | 0 |   | 1                           |        | not(1)                      |

|------------------|---|---|---|--------|----|--------|---|---|---|-----------------------------|--------|-----------------------------|

| $\mathbf{Y}_{i}$ | + | 1 | + | not(1) | +  | not(1) | + | 0 | + | 0                           | +      | 0                           |

|                  | 1 | 0 | 0 | 0      | -1 | 0      | 0 | 0 | 1 | not(1)                      | 0      | not(1)                      |

|                  |   |   |   |        |    |        |   |   |   | $(X_{i-1} \ge 0)e(Y_{i-1})$ |        | $(X_{i-1} \ge 0)e(Y_{i-1})$ |

|                  |   |   |   |        |    |        |   |   |   | $(0 \le_1$                  |        | $_{1}\geq 0)$               |

|                  |   |   |   |        |    |        |   |   | 0 | 1                           | not(1) | 1                           |

|                  |   |   |   |        |    |        |   |   |   | caso contrario              |        | caso contrario              |

|                  | C | S | C | S      | C  | S      | C | S | C | S                           | C      | S                           |

#### **Ejemplo**

Para mostrarlo

0.1.0 not(1)

0.1

$S_{i+1}$

$\frac{X_i}{Y_i}$

$C_{i}$ , el cual es función de los  $X_{i-1}$  e  $Y_{i-1}$  y de los  $X_{i-2}$  e  $Y_{i-2}$ .

Se ve que la lógica a desarrollar toma en cuenta para cada posición los dígitos de la misma y los de las dos posiciones inmediatamente precedentes.

# División de enteros no signados

En la división para un dividendo X de 2n bits y un divisor Y de n bits se tendrán dos resultados de salida; un cociente de n+1 dígitos y un resto de n dígitos tales que

$$x = y \cdot q + r$$

,  $0 \le r < y$

¿Por qué n+1? Recordar que el producto de dos números de n bits podrá dar un resultado de 2n bits o 2n-1 bits. Para este último caso si a uno de los multiplicando o multiplicador lo multiplico por 2 (Paso a n+1 bit). El resultado del producto en tal caso será de 2n bits. Luego si a este lo someto al cociente por el otro factor es claro que el resultado es n+1 bit.

El método normal de papel y lápiz, asumiendo un sistema de números posicional de base b, necesita de un trabajo de suposición. Al primer dígito de q,  $q_n$ , se le da un valor; se calcula el producto  $y.q_n$  y se lo resta a x. Si esta operación produce un valor negativo,  $q_n$  era muy grande y se intenta con otro valor (uno más chico). Si el resultado fuese positivo pero más grande (o igual) que y, entonces  $q_n$  era muy chico y se necesita un valor más grande. El dígito correcto  $q_n$  es tal que:

$$0 \le x - y \cdot q_n \cdot b_n < y \cdot b_n$$

En este proceso de prueba y error voy ajustando el digito del cociente. Una vez que  $q_n$  fue generado, el proceso continua con  $q_{n-1}$  reemplazando x por  $x-y.q_n$  y así hasta obtener  $q_0$ . El último dividendo parcial es el resto r. En la base 2 la división es trivial; probamos si esta contenido. Si esta contenido,  $q_i=1$ , sino simplemente  $q_i=0$  y sigo adelante con la determinación de  $q_{i-1}$ .

La división <u>con restoring</u> plantea hacer la resta si  $\geq 0$ ,  $q_i$ =1 y el resultado es el dividendo para el próximo paso. Si es < 0 (FALLÉ),  $q_i$ =0 y restauro el dividendo para el próximo paso.

## Sean

$$\begin{split} x &= (x_{n\text{-}1}, \, \dots, \, x_0) \\ y &= (y_{n\text{-}1}, \, \dots, \, y_0) \\ q &= (q_{n\text{-}1}, \, \dots, \, q_0) \\ r &= (r_{n\text{-}1}, \, \dots, \, r_0) \end{split}$$

1. Expandir x en  $x' = (x_{2n-2},...,x_{n-1},...,x_0)$ , con  $x_i = 0$ ,  $n \le i \le 2n$ , A 0 (extensión de signo). Cabe aclarar que el hardware está preparado para 2n bits

|       | X |

|-------|---|

| 00000 |   |

2. **for**

$$i=1$$

**step** 1 **until**  $n$  **set**  $z = x' - 2^{n-i}.y$  **if**  $z \ge 0$   $q_{n-i} = 1$  **and**  $x' = z$  **else**

$q_{n-i} = 0$  and not modify x'

$3 \quad r = x^2$

$\xi$ Cómo se ganan posiciones menos significativas? Con los corrimientos a izquierda; comienzo por la más significativa y voy corriendo hasta llegar a la posición 0 (Donde calculo el  $q_0$ )

El "else" del paso 2 es engañosamente simple. Si la resta resulta negativa, tenemos que sumar para restaurar x'. Esto puede evitarse usando una técnica sin restoring. Aunque este último esquema no está limitado al sistema binario, nos restringimos a lo que pasa en él porque es el caso más importante (y para más claridad).

Como dijimos antes las únicas dos alternativas en el sistema binario son 0 y 1. Volviendo al paso 2, cuando z es negativo(cuando suponemos mal), tenemos:

$$x'-2^{n-i}.y\leq 0$$

Luego de la resta, y asumiendo que  $i \neq n$ , sumamos  $2^{n-i}$ . y y restamos  $2^{n-i-1}$ . y, o sea, realizamos:

$$z_1 = x' - 2^{n-i} \cdot y + 2^{n-i} \cdot y - 2^{n-i-1} \cdot y$$

, o

$z_1 = x' - 2^{n-i-1} \cdot y$

Si en su lugar no restauramos z y sumamos  $2^{n-i-1}$ . y cuando z es negativo, obtenemos:

$$z_2 = x' - 2^{n-i} \cdot y + 2^{n-i-1} \cdot y$$

, o

$z_2 = x' - 2^{n-i-1} \cdot y = z_1$

La única dificultad de este método es cuando el último bit el cociente provoca un resto negativo. Esto sucede si tenemos, para algún j:

$$r' = x' - 2^{j+1} \cdot y + (2^j + 2^{j-1} + \dots + 2^0) \cdot y < 0$$

El resto correcto debe haber sido el resto parcial generado al mismo tiempo como el bit  $i^{\underline{mo}}$  del cociente, que es:

$$r = r' + y$$

De esta manera el algoritmo SIN RESTORING para números binarios POSITIVOS queda:

```

1. Expandir x en x' = (x_{2n-2},...,x_n,x_{n-1},...,x_0), con x_i = 0, n \le i \le 2n-2, (extensión de signo) signo = 1

2. for i=1 to n

z = x' - \text{signo.} 2^{n-i}.y

if <math>z \ge 0

q_{n+1-i} = 1

\text{signo} = 1

else

q_{n+1-i} = 0

\text{signo} = -1

x' = z

3. if q_0 = 1

r = x'

else

```

#Txt Ref = Estudiar apunte División Rápida SRT brindado por la cátedra

# División con multiplicación repetida

En los sistemas conteniendo multiplicadores de alta velocidad, la división puede realizarse eficientemente y a bajo costo utilizando repetidas multiplicaciones. En cada iteración, se genera un factor  $F_i$  y se usa para multiplicar el divisor V y el dividendo D. Es elegido de manera que la secuencia  $V \times F_0 \times F_1 \times F_2$  ... converja rápidamente a 1. Esto implica que  $D \times F_0 \times F_1 \times F_2$  ... converge hacia el cociente buscado Q, ya que:

$$Q = \frac{D \times F_0 \times F_1 \times F_2 \cdots}{V \times F_0 \times F_1 \times F_2 \cdots}$$

Si el denominador converge hacia 1, el numerador lo hace hacia Q.

La convergencia del método depende de la elección de los  $F_i$ s. Para simplificar, asumamos que D y V son fracciones positivas normalizadas tales que V = 1 - x, donde x < 1. Poner  $F_0 = 1 + x$ . Ahora podemos escribir:

$$V \times F_0 = (1-x)(1+x) = 1-x^2$$

Claramente  $V \times F_0$  está más cerca de 1 que V. Después poner  $F_1 = 1 + x^2$ . Luego:

$$V \times F_0 \times F_1 = (1 - x^2)(1 + x^2) = 1 - x^4$$

y así sucesivamente. Vi denota  $V \times F_0 \times F_1 \times ... \times F_i$ . El factor de multiplicación en cada etapa se computa como sigue:

$$F_i = 2 - V_{i-1}$$

lo cual es simplemente el 2 complemento de  $V_{i-1}$ . Sigue  $F_i = 1 + x^2$  y  $V_i = 1 - x^{2^{i+1}}$ . A medida que i aumenta,  $V_i$  converge rápidamente a 1. El proceso termina cuando  $V_i = 0.11$  ... 11, el número más cercano a 1 para el tamaño de palabra dado.

# Capítulo 3 - Pipeline

#### Introducción

La alternativa para reducir el tiempo empleado en una dada operación (tarea) es <u>concurrencia.</u> Para ello tenemos dos alternativas:

- Paralelismo: duplicar recursos para realizar actividades simultáneas e independientes.

- Pipelining u Overlap: implica dividir una tarea en subtareas, dedicando un hardware específico a cada una de ellas, etapa o segmento del pipeline y alcanzar una ejecución "solapada" de distintas tareas cada una en distinta fase de ejecución.

Este concepto de pipelining es asimilable a una línea de montaje.

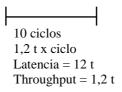

El objetivo del pipe es <u>throughput</u> (cantidad de trabajo por cantidad de tiempo). El throughput del pipeline es determinado por la frecuencia con la que una instrucción sale del pipeline. El tiempo requerido para mover una instrucción de una etapa a otra se llama ciclo de máquina. Con frecuencia un ciclo máquina es un ciclo de reloj (a veces más).

Observar que en general funciona de manera antagónica con otro concepto que es <u>latencia</u>. (tiempo que media entre el inicio y la culminación de una tarea).

La operación del pipe es sincrónica. Debe observarse que se avanza a la velocidad de la etapa más lenta.

#### **Ejemplo**

Otra cuestión a remarcar es que independientemente de la profundidad del pipe (numero de etapas o segmentos) en régimen se obtendrá un resultado por ciclo.

# Requisitos para organizar un pipeline

- a) Dividir en subtareas una tarea de forma tal que la ejecución secuencial de las mismas resulte equivalente.

- b) Disponer para cada subtarea de hardware específico, conocido como etapa o segmento del pipe (Para posibilitar overlap)

- c) Solo hay intercambio de información entre la salida de una etapa y la entrada de la siguiente (en secuencia). No intercambian información interna.

- d) Cada etapa dura aproximadamente lo mismo. Se avanza a la velocidad de la etapa más lenta por lo que se puede constituir en un cuello de botella afectando la performance.

- e) A las etapas hay que aislarlas entre sí para posibilitar el avance discontinuo de la información. Para ello si no tienen memoria propia habría que incorporar buffers inter-etapa.

Tiempo de ejecución de n tareas T = (k-1)t + t n T es el periodo, tiempo de la etapa más lenta ¿Cuál sería el throughput? 1/t

# SpeedUp (k etapas, n operaciones)

La performance ideal en un pipeline se mide por la ganancia de velocidad contra una máquina sin pipeline:

$S_k = \frac{\text{Promedio de Tiempo de instrucciones sin pipeline}}{\text{Promedio de Tiempo de instrucciones con pipeline}} = \frac{T_1}{T_k} = \frac{n \cdot k \cdot t}{((k-1) + n)t} = \frac{n \cdot k}{k - 1 + n}$

Está claro que si n >> k entonces  $S_k \rightarrow k$

# Esquema de los datos que fluyen en el pipe

| S4 |   |   |   | Α | В |  |

|----|---|---|---|---|---|--|

| S3 |   |   | Α | В | C |  |

| S2 |   | Α | В | C | D |  |

| S1 | Α | В | С | D | Е |  |

# Clasificación del pipeline

De acuerdo al uso:

- Datos individuales o Pipeline Aritmético. Estructura las unidades funcionales (ALU) en pipeline, con lo cual solapamos el procesamiento sobre distintos datos. Las unidades lógicas pueden ser segmentadas para operaciones de pipeline.

- **Pipeline de Instrucciones**. Estructura el CPU en pipeline. Se divide el procesamiento de una instrucción en fases, se asigna hardware específico a cada fase y luego se acomete el procesamiento concurrente de múltiples instrucciones. En un comienzo se lo refirió como "look-ahead de instrucciones". Este tipo de pipelining busca explotar el paralelismo a nivel de instrucciones (I.L.P.)

- *Procesos completos*. Aplica pipelining a nivel de múltiples procesadores, cada uno a cargo de un determinado proceso y los resultados de uno serán consumidos por el siguiente en secuencia.

Según las <u>configuraciones</u> y las <u>estrategias de control</u> tenemos 3 clasificaciones:

- *Unifuncional vs. Multifuncional*. El unifuncional siempre es estático ya que posee una función "fijada". Los multifuncionales pueden realizar diferentes tareas, bien sea simultáneamente o en distintos tiempos. Obviamente las tareas se soportan variando la interconexión entre etapas.

- Estáticos vs. Dinámicos (configuración). Los estáticos realizan una función y admiten una configuración por vez. Podrían ser unifuncionales o multifuncionales en cuyo caso una sola configuración por vez. Lo podemos referir como multifuncional estáticamente configurado. Esta alternativa será provechosa en tanto los cambios de configuración sean poco frecuentes. El pipelining dinámico permite que varias configuraciones existan simultáneamente. Claramente debe ser multifuncional. Sin embargo este requiere de un control más sofisticado que los static.

- Escalar vs. Vectorial. Depende del tipo de instrucciones, o del tipo de datos.

- Escalares. Procesa una secuencia de operandos escalares bajo el control del software (do, loop).

- ➤ Vectorial. Tiene instrucciones para operar con vectores, luego la sucesión de operaciones sobre los componentes escalares de los vectores se manejan a través de hardware o firmware. Deberá ser configurado para cada operación, aunque sean las mismas, dado que se los instruye además de la operación, respecto a la ubicación de los vectores, dimensión, etc. Ej. Pipeline multifuncional estáticamente configurado. Por caso, un procesador vectorial tiene un ISA que entiende operaciones vectoriales.

# Secuenciamiento del pipeline

# Pipeline Estáticos

En los pipelines lineales, se sigue una secuencia y cada etapa a lo sumo se visita una vez. En otras palabras <u>no hay feedback ni feedfoward.</u> Luego el Secuenciamiento es trivial. Lo único que hay que contemplar para su temporizado es el tiempo de la etapa más lenta.

En cada nuevo ciclo podría realizar una nueva tarea. Ese no es el caso de un pipe no lineal (en don de que alguna o algunas etapas podrán usarse más de un ciclo).

La tarea es alcanzar regímenes óptimos <u>libres</u> de colisiones.

El primer paso es construir la tabla de reservación. La misma constituye un método para el secuenciamiento óptimo de un pipeline estáticamente configurado.

- Tantas filas como etapas.

- Tantas columnas como ciclos de reloj consuma una operación.

- Tendrá una marca para indicar la ocupación de una dada etapa en un determinado ciclo.

#### **Ejemplo**

|           | 1 | 2 | 3 | 4 | 5 | 6 |

|-----------|---|---|---|---|---|---|

| S1        | X |   |   |   | X |   |

| S2        |   | X |   |   |   | X |

| <i>S3</i> |   |   | X |   |   |   |

| <i>S4</i> |   |   |   | X |   |   |

La posibilidad de colisionar en una etapa la da la presencia de múltiples cruces en una fila.

Si hubiera múltiples cruces en una columna en ningún caso indica posible colisión, solo que en ese ciclo el <u>dato</u> hace uso de más de una etapa.

¿Cuándo habrá colisión?

Si dos iniciaciones entran separadas en ciclos en lo mismo que separa a dos cruces en una fila en algún momento se producen colisiones.

Esas latencias (intervalo entre iniciaciones) son prohibidas o criticas.

Con ellas construimos un vector de colisiones C con una cardinalidad dada por la mayor latencia crítica.

$C = (C_n, C_{n-1}, ..., C_1)$

Donde

$C_i = 1$  si prohibida

$C_i = 0$  en otro caso.

En nuestro ejemplo: C = (1,0,0,0 [la 1])

Con este vector construimos un diagrama de inicializaciones exhaustivo que exponga todos los <u>ciclos</u> posibles "libres de colision".

La idea de ciclo es un camino cerrado que recorra una serie de estados.

El ciclo que recorrimos se caracteriza porque cada nueva iniciación es con la latencia mínima permitida, en particular, se lo conoce como Greedy.

No por ser Greedy asegura la menor latencia promedio. Un ciclo Greedy no podrá tener una latencia mayor que el numero de 1's en el vector de colisión +1.

## Pipeline de instrucciones

Busca un aprovecho del paralelismo a nivel de instrucciones, ILP por sus siglas en inglés.

# Pipeline de instrucciones

#### **Procesador DLX**

Refleja el estado de las arquitecturas <u>RISC</u> al principio de los '90. Fue desarrollado por Hennesey y Patterson. Características:

- Instrucciones de tamaño fijo (32 bits).

- Formato fijo.

- RAR (registro a registro), solo load/store con memoria.

RISC proviene de reduced instrution set computer. Es reducido a nivel de complejidad no de número de instrucciones. RISC favorece el desarrollo de <u>organizaciones</u> del CPU más eficientes, esto es, proporcionan ventajas en orden a reducir CPI (ciclos por instrucciones). Complementariamente, IPC proviene de instrucciones por ciclo. Además facilitan las mejoras a nivel de "<u>microarquitectura</u>". Se buscaba reducción del CPI o aumento del IPC.

# Formato de Instrucciones DLX

I-TYPE

| 6      | 5   | 5  | 16        |

|--------|-----|----|-----------|

| OPCODE | Rs1 | Rd | INMEDIATO |

Se codifican LOAD v STORE

Todas las operaciones inmediato (Rd ← Rs1 op inmediato

R-TYPE

| 6      | 5   | 5   | 5  | 11      |

|--------|-----|-----|----|---------|

| OPCODE | Rs1 | Rs2 | Rd | FUNCION |

ALU Operation Rd ← Rs1 op Rs2

J-TYPE

| 6      | 26                  |  |  |  |

|--------|---------------------|--|--|--|

| OPCODE | OFFSET (SUMA AL PC) |  |  |  |

Jump and Jump and link

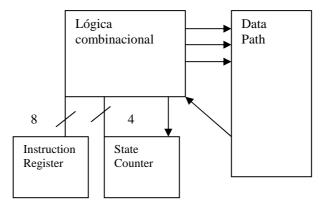

#### **Data Path**

Es la parte del CPU en donde se almacenan, se procesan, se comunican los datos dentro del mismo.

Es el responsable de la performance última alcanzable.

Por otro lado, el <u>control path</u> es responsable de organizar la secuencia de señales de control que activando sobre el data path posibilitan la ejecución de las distintas instrucciones. Debe asegurar la "correctitud" de las mismas en algún sentido es "la parte inteligente del CPU."

# Pipeline de Instrucciones para DLX

Asumamos que el procesamiento de cada instrucción requiere los siguientes 5 pasos.

1. *Instrucción Fetch*. Se envía el PC y se trae la instrucción de memoria poniéndola en el IR (registro de instrucción).

$MAR \leftarrow PC; IR \leftarrow M[MDR]$

2. *Instrucción Decode/Register Fetch*. Se decodifica la instrucción y accede al register file para leer los registros (operandos). También se incrementa el PC para apuntar a la próxima instrucción. La decodificación puede ser hecha en paralelo junto a la lectura de los registros. Esto puede lograrse gracias al formato fijo de las instrucciones.

$A \leftarrow Rs1$ ;  $B \leftarrow Rs2$ ;  $PC \leftarrow PC + 4$  (avanzo 32 bits, 4 bytes)

- 3. *Ejecución / Cálculo dirección efectiva*. La ALU opera con los operandos de la etapa anterior realizando una de las siguientes tres funciones:

- Referencia a memoria. La ALU suma los operandos para formar la dirección efectiva y el MDR es cargado si es un store.

MAR  $\leftarrow$  A +  $(IR_{16})^{16}$  ##  $IR_{16..31}$  campo inmediato con extensión de signo.

Si es un store MDR  $\leftarrow$  B

- ALU instrucción. La ALU realiza la operación especificada por el opcode.

ALU OUTPUT (C)  $\leftarrow$  A op (B o (IR<sub>16</sub>)<sup>16</sup> ## IR<sub>16..31</sub>)

- Branch/Jump. La ALU suma el PC con el valor inmediato para computar la dirección del target del jump. Si es un branch, un registro, que ha sido leído en la etapa anterior, es chequeado para decidir si la dirección debe ser insertada en el PC.

Si es un jump:

ALU OUTPUT (C)  $\leftarrow$  PC +  $(IR_{16})^{16}$  ##  $IR_{16..31}$

Si es un branch (salto condicional)

COND  $\leftarrow$  (A op 0)

- 4. Acceso a Memoria/Completado del branch. Realiza una de las siguientes operaciones:

- Referencia a Memoria. Si la instrucción es un load, los datos son retornados de memoria. Si un store los datos son escritos en memoria.

$MDR \leftarrow M[MAR]$  Si LOAD  $M[MAR] \leftarrow MDR$  Si STORE

- Branch. Si es un branch, el PC es reemplazado por la dirección destino del branch. if(COND) { PC ← ALU OUTPUT(C)};

5. Write Back. Escribe el resultado en el register file, ya sea que venga de memoria o de la ALU.

RD ← ALU OUTPUT (C) O MDR

Para reducir el tiempo de fetch se pueda utilizar un buffer para realizar un look-ahead de instrucciones.

De forma independiente de la actividad del CPU (ejecutando) ir a memoria y buscar las instrucciones <u>por adelantado</u>. Así, procesadores elementales como 8086 tenían un buffer de 6 bytes y el 8088 de 8 bytes. Mejor aún es un buffer con look-ahead y con look-behind.

Este concepto resulta "sublimado" con la utilización de la memoria cache.

#### **DECODE**

En esta etapa se realiza la búsqueda de operandos. Se acelera si los operandos los manejamos en registros. El acceso a registros es en menor tiempo que a memoria por dos factores:

- a) No existe cálculo de dirección efectiva

- b) Aunque se emplee cache (memoria rápida, tanto para instrucciones como para datos) y a pesar de usar la misma tecnología que los registros, estos últimos son más rápidos porque son de mucho menor tamaño.

#### **EXECUTE**

Aquí se busca la mejora del algoritmo y de la implementación. Interesa favorecer el uso de unidades funcionales dedicadas (no multipropósito). Además al tener diferentes unidades podre hacer un uso concurrente de estas, ganando así velocidad.

El paso siguiente, en orden a mejorar el tiempo de ejecución de los programas es Pipelining.

En una situación ideal el tiempo de ejecución por instrucción seria:

# Tiempo por instrucción en una maquina **no** pipelined K(n° de etapas del pipeline)

Este límite no será alcanzable en general por dos cuestiones, a saber:

- a) la dificultad en alcanzar tiempos iguales por etapa

- b) los latch interetapa

#### **Ejemplo**

El DLX estructurado en 5 etapas:

| IF  | inst i | IF | ID | EX | MEM | WB  |     |     |     |    |

|-----|--------|----|----|----|-----|-----|-----|-----|-----|----|

| ID  | i+1    |    | IF | ID | EX  | MEM | WB  |     |     |    |

| EX  | i+2    |    |    | IF | ID  | EX  | MEM | WB  |     |    |

| MEM | i+3    |    |    |    | IF  | ID  | EX  | MEM | WB  |    |

| WB  |        |    |    |    |     | IF  | ID  | EX  | MEM | WB |

|     |        | 1  | 2  | 3  | 4   | 5   | 6   | 7   | 8   | 9  |

#### **Ejemplo**

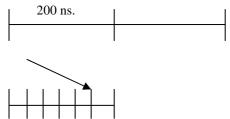

El tiempo seria (en orden) (IF, ID, EX, MEM, WB) [50 ns, 50 ns, 50 ns, 50 ns, 50 ns] y 5 ns latch interetapa.

Tiempo por instrucciones sin pipe = 50 + 50 + 60 + 50 + 50 = 260 ns

Para el pipe, el tiempo de ciclo seria: 60 + 5 = etapa más lenta + latch = 65

SpeedUp =  $\frac{\text{Tiempo de ejecución sin pipe}}{\text{Tiempo de ejecución sin pipe}} = \frac{260}{65} = 4 \text{ veces (no 5)}$

Tiempo de ejecución con pipe 65

#### Requerimientos básicos para estructurar un CPU con pipeline:

- a) Toda vez que una etapa no cuente con su memoria (local) deberá introducir buffer a la entrada

- b) Todo recurso que es usado en más de una etapa o bien se modifica o alternativamente se duplica (permite solapamiento)

- c) Todo dato que es usado más adelante en el pipe (más allá de la etapa siguiente) deberá ser convenientemente buffereado.

- d) En cuanto a la profundidad del pipe, esto <u>no</u> podrá ser arbitrariamente profundo, habida cuenta que para asegurar la fluidez hay ciertas operaciones que tienen que ser atómicas, esto es, resolverse en un ciclo de reloj. Por caso, la operación básica de suma (resta).

A continuación indico los eventos en cada etapa del pipe

| STAGE | ALU INST.                          | LOAD OR STORE INST                        | BRANCH INST                     |

|-------|------------------------------------|-------------------------------------------|---------------------------------|

| IF    | $IR \leftarrow M[PC]$              | $IR \leftarrow M[PC]$                     | $IR \leftarrow M[PC]$           |

|       | PC ← PC + 4                        | PC <b>←</b> PC + 4                        | PC <b>←</b> PC + 4              |

| ID    | A ← Rs1                            | A ← Rs1                                   | A ← Rs1                         |

|       | B ← Rs2                            | B ← Rs2                                   | B <b>←</b> Rs2                  |

|       | PC1 ← PC                           | PC1 ← PC                                  | PC1 ← PC                        |

|       | IR1 ← IR                           | IR1 ← IR                                  | IR1 ← IR                        |

| EX    | ALU OUTPUT (C) $\leftarrow$ A op B | $MAR \leftarrow A + (IR_{16})^{16} \# \#$ | ALU OUTPUT1 ← PC1 +             |

|       | ALU OUTPUT (C) $\leftarrow$ A op   | IR <sub>1631</sub>                        | $(IR_{16})^{16}$ ## $IR_{1631}$ |

|       | $(IR_{16})^{16}$ ## $IR_{1631}$    | SMDR ← B                                  | COND $\leftarrow$ Rs1 op 0      |

|       | Rd2 ← Rd1                          |                                           | _                               |

| MEM   | ALU OUTPUT1 ← ALU                  | $LMDR \leftarrow M[MAR]; OR$              | IF(COND)                        |

|       | OUTPUT                             | $M[MAR] \leftarrow SMDR$                  | PC ← ALU OUTPUT (C)             |

|       | Rd3 ← Rd2*                         |                                           |                                 |

WB Rd3 ← ALU OUTPUT1 Rd3 ← LMDR

Al MDR lo debo duplicar, tendré LMDR (para load) y SMDR (para store).

El campo que identifica el registro destino, según vimos con los formatos de instrucción podrá ocupar 2 lugares distintos  $IR_{20-16}$ . $\acute{o}$   $IR_{16-11}$

Asumo que el banco de registros tiene 2 pórticos de lectura y un pórtico de escritura.

Sin pipe 2 accesos a memoria cada 5 ciclos

Con pipe 2 acceso a memoria por ciclo

Con cache independiente busco instrucciones y datos en el mismo ciclo

# **Pipeline Hazzard**

Hay situaciones que <u>podrán</u> apartar al pipe de la performance ideal (un IPC=1 o un CPI=1)

Estas situaciones se conocen como "Hazzards", riesgos, los cuales en general se detectan en la etapa decode.

Los hazards "provienen", son atributos del código (programa). Estos podrán o no traducirse en perdida de performance de la organización (o microarquitectura).

Hay tres tipos de hazzards:

- Estructural: Se produce si alguna combinación de instrucciones no puede aceptarse debido a conflicto de recursos, o sea, una instrucción en la etapa decode requiere recursos que están siendo afectados por instrucciones previas en el pipeline. El HW no puede soportar todas las posibles configuraciones de instrucciones.

- **Datos**: Se da si no hay independencia de rango-dominio entre las instrucciones. En etapa decode e instrucciones previas que aun no finalizaron su ejecución. La idea es que el resultado de la ejecución sea el mismo del que se alcanza con una simple ejecución secuencial.

- **Control:** Aparecen a partir de instrucciones que cambian el flujo secuencial de las mismas. Ejemplo de esto: Jump, Branch, Call, Return.

Si en la etapa decode se detecta un hazzard y este no está resuelto (a nivel de microarquitectura) el recurso de mínima (de hardware) es pipeline interlock.

Este <u>frena</u> al pipeline, no se sigue haciendo el fetch, y consecuentemente nada con las instrucciones siguientes, permitiendo que las previas en el pipeline avancen normalmente.

Recién cuando desaparezca el conflicto se libera el procesamiento de las nuevas instrucciones.

Esto es tan así porque la decodificación es en orden, lo cual es crítico que sea así.

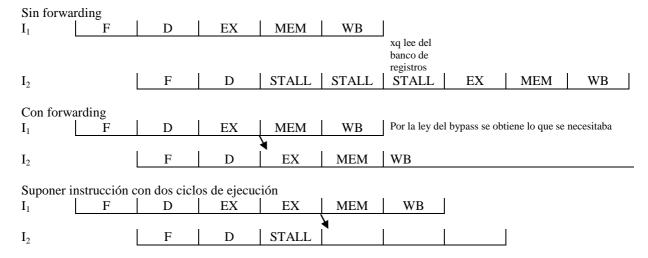

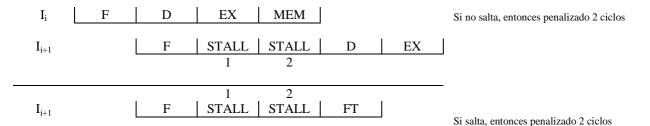

Esto da lugar a ciclos "STALL". Estos ciclos perdidos son asimilables a "burbujas" que viajan en el pipe.

| $I_i$        | F | D | EX | M     | WB    |    |    |    |    |

|--------------|---|---|----|-------|-------|----|----|----|----|

| $I_{i+1}$    |   | F | D  | STALL | STALL | EX | M  | WB |    |

| 111          |   |   |    |       |       |    |    |    | =  |

| $I_{i+2} \\$ |   |   | F  | STALL | STALL | D  | EX | M  | WB |

¿En que se traducen los ciclos stall's? En un apartamiento del CPI = 1

$$CPI_{c/pipe} = CPI_{ideal} + ciclos stall por instruccion.$$

$$\begin{array}{ll} CPI_{ideal} & = & \underline{CPI_{s/pipe}} \\ & Profundidad \ del \ pipe \end{array}$$

Realizo sustitución:

Simplificando, esto es, sin considerar lo relativo a periodo de reloj con y sin pipe:

CPIideal + stall por instrucción

Resulta claro que sin stall's el SpeedUp está dado por el pipeline depth, es decir, el numero de etapas. Cabe aclarar que cuanto mayor sea la profundidad del pipe mayor podrá ser los ciclos stall por instrucción.

#### **Hazard estructurales**

En general una alternativa es "aumentar" el recurso en cuestión (como sería el caso del renombramiento de registros). En particular a nivel de unidad funcional se tienen tres alternativas para entender con esto (esto se podrá dar si la ejecución demanda más de un ciclo).

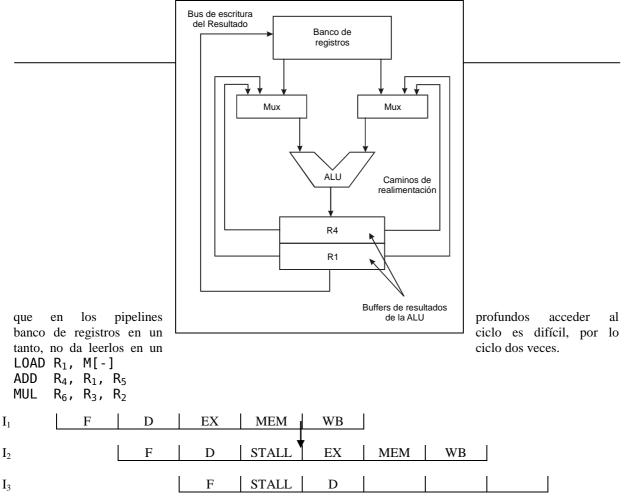

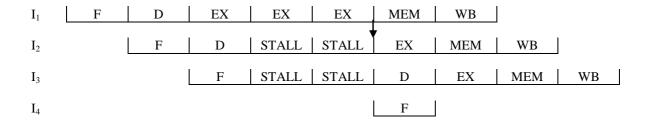

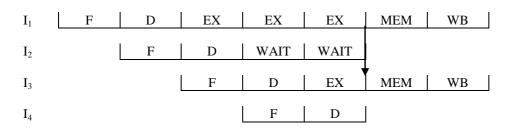

- a) Agregar unidades funcionales que podrán operar en paralelo.

- b) Pipeline de la unidad funcional que operan de forma solapada